Firstly Happy New Year to all our blog readers !!!

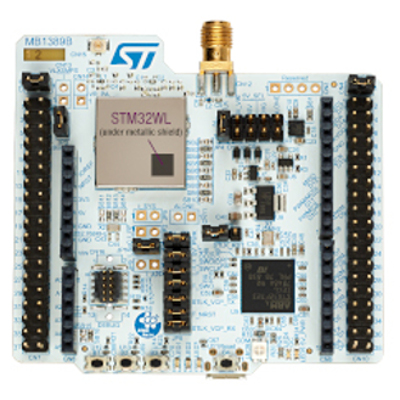

We’ve been a bit quiet of late on this blog as we have been snowed under with work however we thought we would talk about a very exciting new development from ST Microelectronics – this week demonstrating at CES2020 in Las Vegas a recently released exciting new STM32WLE5 microcontroller SoC with an ARM Cortex M4 core coupled with a Semtech SX126x on the same silicon die – part of the STM32WLEx family. There are other LoRa SoC microcontrollers on the market at the moment, however they contain separate microcontroller and Semtech SX127x LoRa transceiver die under one roof. Also due to the frequency range of SX127x devices, different parts are needed depending on the local regulatory frequency requirements e.g. 868MHz for EU, 915MHz for USA, even 433MHz for some countries. The STM32WL avoids this by utilising a more recently SX126x LoRa transceiver from Semtech which has a wider frequency range of 150-960MHz and better radio specification compared to SX127x such as an extra 10dBm sensitivity, 5dB link budget, half the power consumption in receive mode and interestingly a new spreading factor (SF5) for dense radio networks. Also alternative modulation schemes are supported such as (G)FSK, (G)MSK and BPSK (allowing use of Sigfox for example).

Tightly coupled on the same die is a ARM Cortex M4 microcontroller that really unleashes the possibilities of IoT devices – previous SoC’s usually are powered by a Cortex M0 or M0+, which whilst an awesome device is often limited in computational power and RAM/FLASH storage. For example, recently ARM have added support to the M4 for Google’s TensorFlowLite and uTensor, helping further bring edge AI to the IoT. The STM32WL incorporates up to 256kB of FLASH and 64kB for to allow firmware development without resource limit worries, reduced wake-up time in less than 5us using an internal LDO which switches to DCDC once the device has completely started up, on-board hardware crypto capability, as well as a plethora of other peripherals including two SPIs, three I2Cs, a low power UART, two UARts, seven 16 and 32 bit timers, 12 bit ADC and DACs and 43 GPIOs. Ultra low power capability is enhanced by a standby current draw of 71nA and deep sleep of 5nA.

We are awaiting price information and hope to get our hands on an engineering sample soon !!!